|

|

|

Wave-pipelining

project "Shaping The Waves"

This project

follows the idea of System Hyper

Pipelining

(SHP) and combines it with

wave-pipelining.

SHP generates interleaved-multithreaded designs and replaces original

registers with memories to allow dynamic interleaved-multithreaded scheduling (threads

can be stalled and therefore reordered).

SHP also uses C-Slow Retiming.

But instead of inserting "C-1" registers

into each path, wave-pipelining is used in this project.

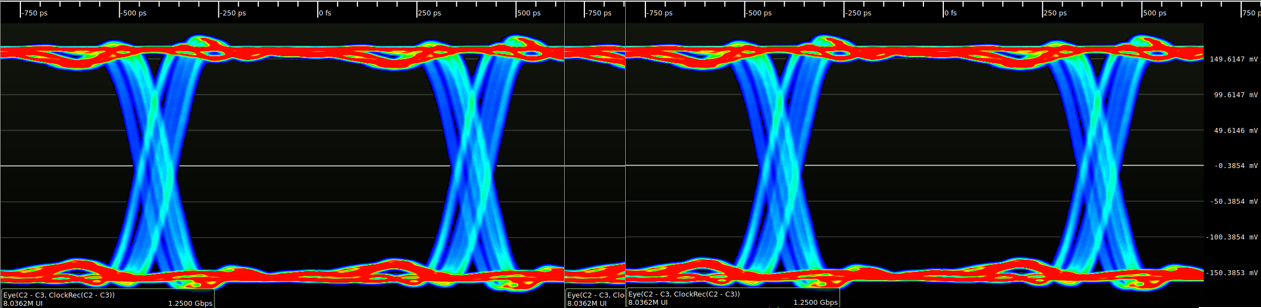

Fig. 1. Wave-pipelining, all paths in a design must have equal length

Wave-pipelining requires equal length between the relevant registers.

Multiple waves travel through the logic during execution. More

information on this rather old idea of wave-pipelining can be found in

this paper [1].

[1] W. Burleson, M. Ciesielski, F. Klass, and W. Liu, "Wave-Pipelining:

A Tutorial and Research Survey", IEEE Trans. on VLSI, vol. 6, no. 3,

Sept. 1998, link: https://www.cs.princeton.edu/courses/archive/fall01/cs597a/wave.pdf

The project is very similar to the Arduissimo

project, which follows

the same idea but is optimized for FPGA technology. The ASIC version

now uses wave-pipelining instead of register insertion and has only one

RISC-V

core implemented (instead of 4).

The ASIC project "Shaping The Waves" is defined by:

- System-Hyper-Pipelined

MiniSoC

- 232

MHz running 3 waves 8 independent threads

- RV32iMC-P3C4D8W3

- 3

classical Pipeline stages

- 4

Copies running at the same time

- memory

thread Depth is 8

- 3

Waves maximum

- Timer

with 128 programmable events

- 32

GPIOs with programmable trigger-units

for SW-defined protocols

- SkyWater

0,13µm, Efabless Shuttle 8

- OpenSource

tools: Caravel\OpenLane

- Sponsored

by Efabless and Google !!!

The

project can be

found on github here.

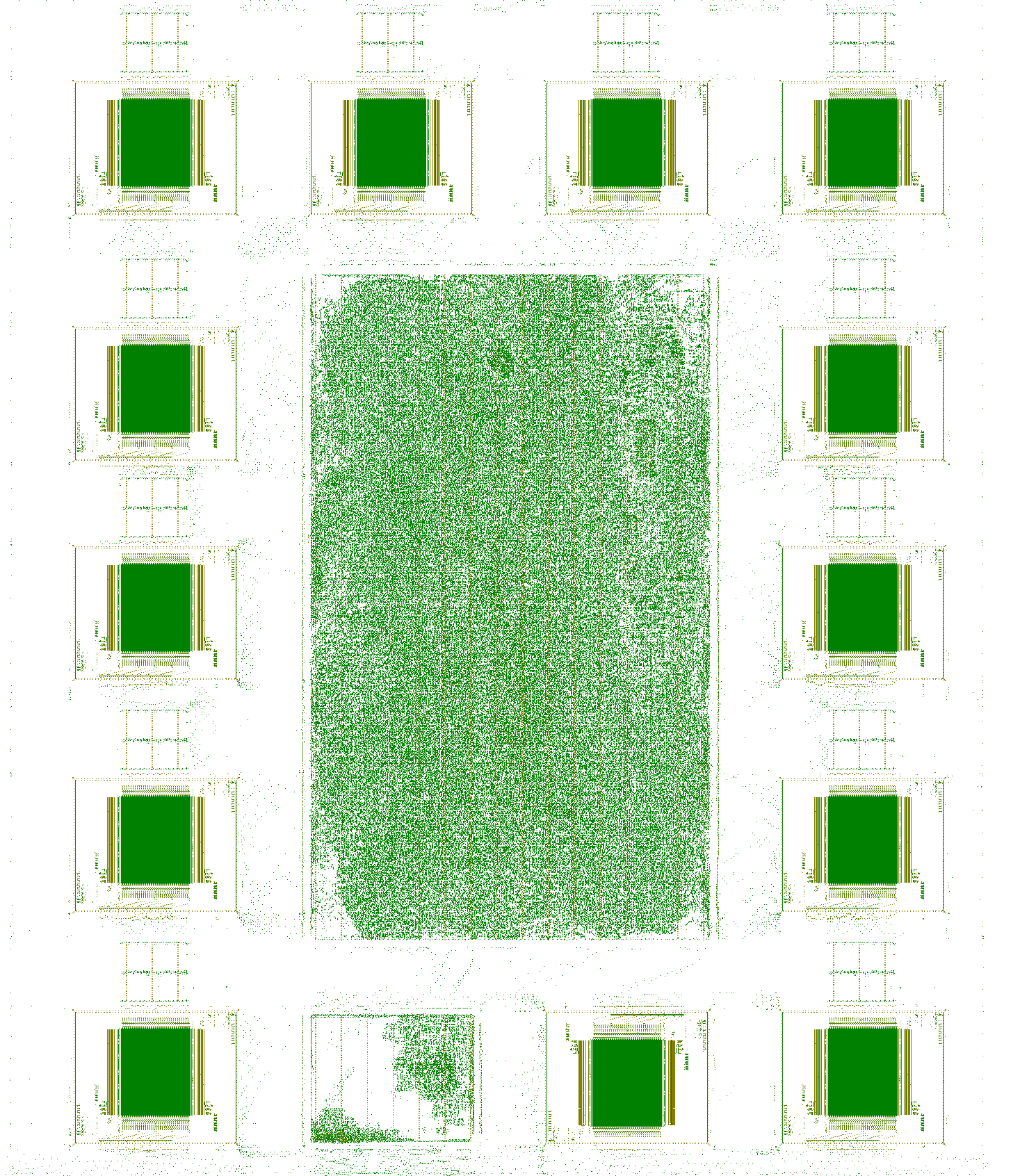

The following Figure

shows the ASIC

implementation:

Fig. 2. ASIC layout

of the project

| last

modified: 2023/Mar/22 |

|

|

|

|

|

|